面向系统级ESD仿真的构件建模

问:为什么ESD目标级工业委员会提倡使用类似SPICE的电路模拟来评估系统级的ESD可靠性?

答:这是一种省时的选择,可以先找出ESD资格测试时出现的问题,然后通过低效的试错程序来纠正这些问题。利用电路仿真对系统ESD可靠性进行虚拟样机设计,称为系统高效ESD设计,或SEED。

问:系统级ESD模拟的障碍是什么?

答:微电子元器件供应商一般不提供其零部件的ESD型号。

问:有没有提出解决办法?

答:有人认为,经验模型可以适用于TLP(传输线脉冲)I-V测量数据[1]。

问:这些经验模型是如何分类的?

答:大多数是分段线性模型。还研究了更先进的非线性模型,如递归神经网络。

为了模拟系统级ESD,必须模拟沿放电路径的所有微电子元件;这些元件可能包括瞬态电压抑制器、铁氧体扼流圈或其他离散元件。本文主要研究集成电路元件。如果以合理的精度模拟集成电路引脚处的静电感应电压和电流波形,就可以检查该部件是否会被驱动到其安全工作区域之外,还是会发生热故障。这种分析足以确定集成电路在ESD资格测试中是否会避免硬故障。

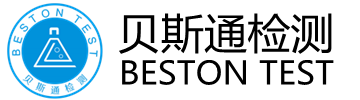

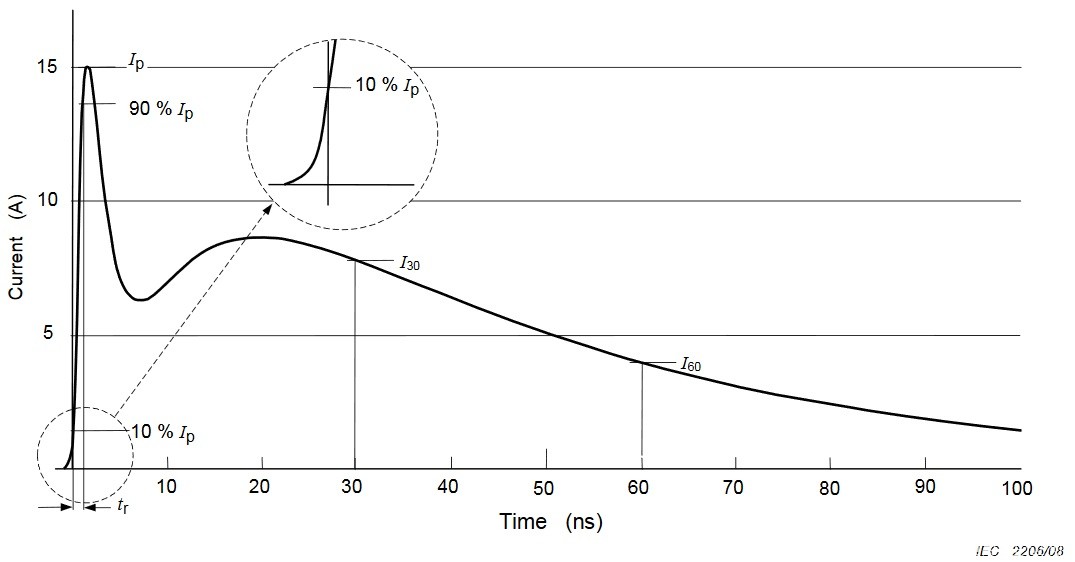

元件对ESD的响应通常用传输线脉冲(TLP)测试来评估。脉冲I-V曲线应在电源和电源状态下测量,这就要求被测试的设备,即IC,安装在带有电源的测试板上。参考文献,包含一个测试板设计示例。通常,脉冲I-V曲线适合于分段线性模型.生成的模型是静态模型,因为I-V曲线不能提供被测设备的动态响应信息。

如果集成电路的瞬态响应是线性的,那么在原则上,静态模型可以用S参数测量得到的瞬态模型来扩展。在许多情况下,集成电路的瞬态静电放电响应主要由封装的寄生电感和电容元件控制。在这种情况下,可能不需要做任何测量来获得瞬态模型,因为许多IC供应商提供的IBIS模型包括对包的描述。从TLP测量得到的分段线性模型和RLC封装模型可以连接在一起,形成一个完整的ESD组件模型[7],如图1所示。

一个由静态I-V模型和封装模型组成的组件模型很好地预测了集成电路对tlp测试仪产生的方型电流脉冲的瞬态响应,但不是全部。这一发现表明,片上半导体器件的动态非线性响应并不总是被封装阻抗的动态响应所掩盖。

在测量数据的基础上建立芯片对静电放电动态响应的精确模型,即封装的集成电路对ESD型电流脉冲的瞬态响应是非常困难的,部分原因是当集成电路安装在电路板上时,无法精确地将探针放置在IC输入端。IC设计人员可以更容易地创建组件ESD模型。

设计者的模型将包括芯片Netlist,以及设备的紧凑模型;例如,IC供应商不愿意向他们的客户提供这类模型,因为这些模型可能会披露知识产权(IP)。准确的瞬态模型能否被重新表示为IP模糊行为模型是值得考虑的问题。其中一个候选模型是递归神经网络。

递归神经网络(RNN)是非线性状态空间系统的一种通用逼近器,这类系统由常微分方程描述。RNN特别适合处理时间序列数据,例如实验室仪器或电路模拟器提供的数据。IC IO引脚的RNN模型

输入,u,可以是电流或电压,以及输出,y是另一个量,即电压或电流。WrWuWy , bu 和by是模型参数。x 表示系统的内部状态。例如,如果被建模的系统是单个二极管,则变量映射可能是电压为u,存储电荷x,以及当前的y。实际上,用户没有指定从物理量到RNN模型内部状态的映射;相反,内部状态是从数据中“学习”出来的,不需要与可识别的物理量相对应。图2提供了RNN的图像视图。

RNN模型可以在Verilog-A中实现,然后使用ADS、HSPICE和谱等商用电路模拟器进行仿真。

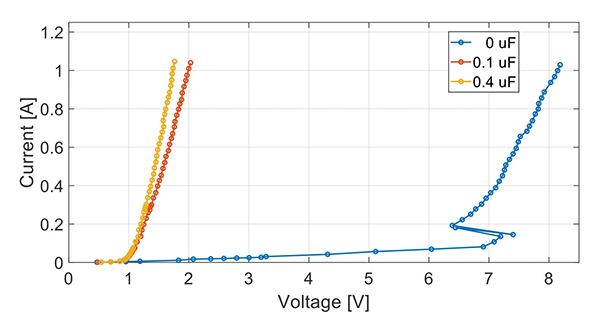

为了说明瞬态行为建模的可行性,通过对全芯片ESD保护网络的Netlist进行仿真,生成训练数据。利用这些数据,利用开源优化软件建立了电路的RNN模型.图3显示了使用电路的Netlist描述和RNN模型获得的仿真结果。与行为模型相关的误差很小,小于3%。应该注意的是,在图3的模拟中应用于电路的刺激没有包括在训练数据中。重要的是要证明一个行为模型是可概括的,也就是说,它预测正确的行为对以前看不见的刺激作出反应。

stimuli

虽然瞬态行为模型的好处是显而易见的,但是需要做更多的工作来确定RNN是否是最适合表示组件的ESD响应的模型。虽然RNN被认为是一个“通用”模型,但它存在一些困难,例如,必须确保所学习的网络对于所有输入刺激都是稳定的。

TLP提供了一个单端口的I-V测量,因此从TLP测量数据中提取的模型是一个单端口模型。需要注意的是,在IC引脚处测量到的脉冲I-V曲线不仅描述了IC,而且还描述了IC和板级电流路径的综合效应。流入IC的IO引脚的电流按受板级电力传输网络(PDN)的阻抗影响的比例在可能的返回路径之间划分。

因此,如图4所示,在IC引脚上测量的I-V特性受板PDN阻抗的影响。如果用组件的多端口ESD模型代替现在使用的单端口模型,则可以在仿真中捕捉到系统电路板的全部效果。即使PDN阻抗太低,板对被测I-V的影响也是可以忽略的,软失效分析可能需要一个多端口的集成电路模型。

在资格测试中,大约一半的系统级ESD故障是软故障。其中许多故障是由于IO引脚上出现的噪音(“小故障”)造成的,这是连接线或封装痕迹之间磁耦合的结果[12]。时域电磁模拟器可以进行噪声耦合分析.假设ESD电流主要以信号引脚进入IC;片上保护网络将ESD电流分流回封装(然后是板)。

因此,芯片上的电路决定了封装键合线或轨迹的组合构成了返回路径,而封装级的噪声耦合模拟应该能够理解芯片的效果。EM模拟器不能提供这样的功能,但是可以使用混合电磁电路模拟器.在[13]中,Speed 2000模拟器被用来模拟ESD诱导的噪声耦合到集成电路封装内的信号线上;示例结果如图5所示。

在过去的5到6年中,工业界和大学的研究人员已经在系统级ESD模拟方面取得了最新进展,本文对其中的一些活动进行了概述。要建立可重复和准确的方法来描述组件对系统级ESD的响应,并就最合适的模型结构达成共识,还有许多工作要做。