为了解决电磁干扰EMI问题,设计工程师还必须遵循一系列的设计规则和方法:

1.在实际设计中建议使用实体地和电源层,避免电源和地被分割,这种分割可能导致复杂的电流环路。电流环路越大辐射也越大,所以必须避免任何信号,尤其是时钟信号在分割地上布线。

2.将时钟驱动器布局在电路板中心位置而不是电路板外围,将时钟驱动器放置在电路板外围会增加磁偶极矩(magnetic dipole moment)。

2.为了进一步降低顶层时钟信号线的EMI,好是在时钟线两侧并行布上地线。当然,好将时钟信号布在地层与电源层之间的内部信号层上。

4.时钟信号使用4mil到8mil的布线宽度,由于窄的信号线更容易增加高频信号衰减,并降低信号线之间的电容性耦合。

5.由于直角布线会增加布线电容并增加阻抗的不连续性,从而导致信号劣化,所以应该尽量避免直角布线和T型布线。

6.尽量满足阻抗匹配。绝大多数情况下,阻抗不匹配会引起反射,而且信号完整性也主要取决于阻抗匹配。

7.时钟信号布线不能并行走得太长,否则会产生重》从而导致EMI增大。一个较好的办法是确保这些线之间的间距不小于线宽。

8.在设计图形存储器子系统时,必须确保时钟线远离任何PC的I/0连接器,距离保持在至少2.5英寸以上。这些连接器包括并行口、串行口、键盘连接器和监视器连接器等。在I/0连接器周围设置地隔离沟的方式可以将共模辐射限制到小。对于高频共模辐射的抑制,推荐使用具有合适阻抗特性的铁氧体器件,由于铁氧体的阻抗随频率而变化,在高频区域铁氧体的特征更接近一个电阻而不是电感,并且铁氧体的电四损耗可用于消除辐射:Tracy6_Mal

9.对外部或内部时钟源使用Vdd去耦电容可以降低EMI,去耦电容的布局对于降低时钟源器件封装的发射来说非常重要,所有电容都应该布局在离vdd管脚20mil的范围以内。去耦电容的值是根据电容的谐振频率来定,对于时钟发生器较高的频率而言,100pF左右的电容比较合适。

10.缩短高频信号布线长度以及减小电流环路面积可有效抑制EMI。同时,在时钟源上设置RC滤波器来控制上升和下降时间可降低EMI,因为较慢的上升和下降时间产生较低的发射频率。

11.确保时钟芯片的电源管脚紧邻地管脚可以使电源环路小化。使电源和地管脚引线并行而且互相靠近,这样可以有效地降低EMI。

12.当信号噪声源不能消除时,采用滤波器可以有效地实现噪声抑制。EMT滤波器以及铁氧体磁珠是常用的滤波器,铁氧体磁珠通过增加电感来抑制高频分量。

采用EMI滤波器消除高频噪声

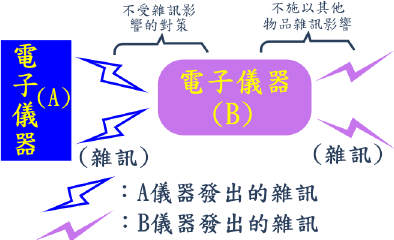

EMI滤波器可以消除电源线上的高频噪声,这种滤波器可以在市场买到,EMl滤波器不仅阻止噪声进入系统,而且也会阻止系统产生的噪声影响系统中的其它部分,具有双向效果。EMI滤波器的构成可以根据节点电阻来确定:高阻抗节点要求使用电容,而低阻抗节点要求使用电感。

EML滤波器的结构还可以是旁路电容、L电路、x型电路和T型电路,采用旁路电容的唯一器件就是电容器,当连接到滤波器的阻抗很高时采用旁路电容是一种很好的选择。

除了时钟电路以外,高速器件也会产生更多的高频噪声,这是因为较短的信号跳变时间会使信号在高频范围上有更多的能量。总之,扩展频谱方法提高了系统EMI性能,可以加速产生信号干扰的产品上市,并且降低封装和屏蔽方面的成本。与此同时,设计工程师应该使用所有可能的方法和设计规则来降低EMI。

本文一共分三篇,其他两篇阅读课点击:

1、采用扩展频谱方法减少EMI同题(上)

2、采用扩展频谱方法减少EMI同题(中)

免费电话:我们